【導讀】48 V配電在數據中心和通信應用中很常見,有許多不同的解決方案可將48 V降壓至中間電壓軌。最簡單的方法可能是降壓拓撲,它可以提供高性能,但功率密度往往不足。使用耦合電感升級多相降壓轉換器可以大幅提高功率密度,這種方案與先進的替代方案不相上下,同時保持了巨大的性能優勢。多相耦合電感的繞組之間反向耦合,因而各相電流中的電流紋波可以相互抵消。這種優勢可以用來換取效率的改善,或者尺寸的減小和功率密度的提高等。

摘要

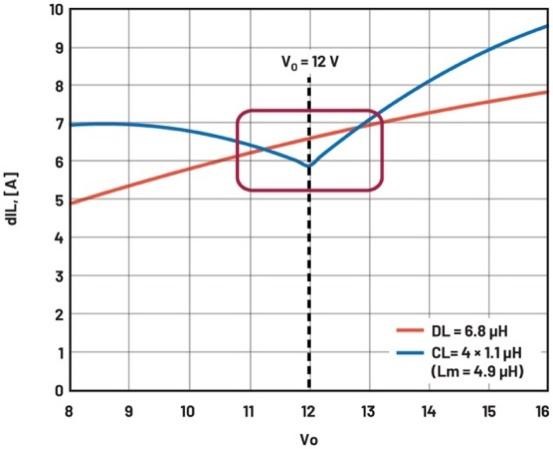

48 V配電在數據中心和通信應用中很常見,有許多不同的解決方案可將48 V降壓至中間電壓軌。最簡單的方法可能是降壓拓撲,它可以提供高性能,但功率密度往往不足。使用耦合電感升級多相降壓轉換器可以大幅提高功率密度,這種方案與先進的替代方案不相上下,同時保持了巨大的性能優勢。多相耦合電感的繞組之間反向耦合,因而各相電流中的電流紋波可以相互抵消。這種優勢可以用來換取效率的改善,或者尺寸的減小和功率密度的提高等。本文介紹了一個示例,其磁元件的體積和重量只有原來的1/4,使得1.2 kW解決方案符合1/8磚的行業標準尺寸,并且峰值效率高于98%。本文還重點討論了如何根據耦合電感的品質因數(FOM)優化48 V拓撲。專注于DC-DC轉換領域的工程師將會對此感興趣。

引言

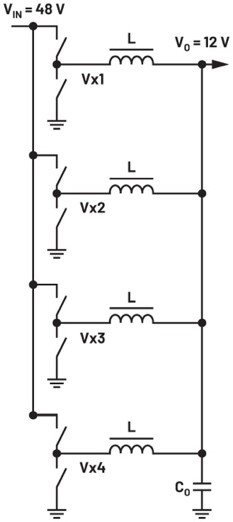

48 V配電軌通常會降壓至某個中間電壓,往往是12 V或更低,然后不同的本地負載點穩壓器直接向不同負載提供各種不同的電壓。對于48 V至12 V降壓調節器,首選之一是多相降壓轉換器(圖1)。這種解決方案提供穩壓VO和快速瞬態性能,很容易實現且成本較低。對于幾百瓦到>1 kW的功率范圍,可以考慮四相并聯。然而,高效率通常是一個優先考慮因素,與12 V甚至5 V輸入的較低電壓應用相比,48 V轉換器為了保持低開關損耗,開關頻率通常相對較低。這會在“伏特×秒”方面對磁元件造成雙重損害,因為已經很明顯的電壓也會作用相對較長的時間。因此,與較低電壓應用相比,48 V的磁元件通常體積較大,并使用多匝繞組來承受顯著提高的“伏特×秒”。48 V降壓轉換器仍然可以實現高效率,但整體尺寸通常相當大,其中電感占據了大部分體積。

基本48 V至12 V ~1 kW降壓轉換器具有四相,使用6.8 μH分立電感,開關頻率為200 kHz。這四個電感是目前最大和最高的元件,占解決方案體積的大部分。本文的目標是保持或提高此初始設計所實現的高效率,但顯著減小磁元件的尺寸。

常規降壓轉換器各相的電流紋波可由公式1求出,其中占空比為D = VO/VIN,VO為輸出電壓,VIN為輸入電壓,L為電感值,Fs為開關頻率。

圖1.使用分立電感的四相降壓轉換器。

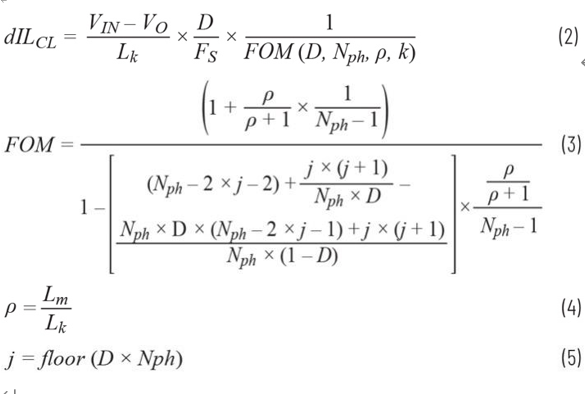

用漏感為Lk且互感為Lm的耦合電感1-7代替分立電感(DL),CL(耦合電感)中的電流紋波可表示為公式2。6 FOM表示為公式3,其中Nph為耦合相數,ρ為耦合系數(公式4),j為運行指數,僅定義占空比的適用區間(公式5)。

CL考慮因素

改進的第一步是針對耦合系數Lm/Lk的幾個實際合理值繪制Nph = 4的FOM曲線(圖2)。紅色曲線Lm/Lk = 0表示分立電感的FOM = 1基線。已經證明,漏感非常低的陷波CL (NCL)結構一般能實現非常高的Lm/Lk,因此FOM值也很高。8,9然而,雖然在理想情況下目標占空比正好位于第一陷波D = 12 V/48 V=0.25,但有必要考慮VIN和VO的某個范圍。有時候,標稱VIN可以是48 V或54 V加上一些容差,VO可以調整為遠離12 V,等等。如果占空比在D = 0.25附近的某個范圍內變化,為使電流紋波始終受到抑制,應選擇具有相當大漏感的典型CL設計,而不是NCL,但FOM值仍然相當大。假設Lm/Lk > 4,與DL基線相比,減小CL中的電感值可能使圖2中的FOM提高約6倍。減少能量存儲會直接影響所需的磁元件體積。因此,將DL = 6.8 μH降低為CL = 1.1 μH應有利于減小尺寸。

圖2.針對一些不同Lm/Lk值,4相CL的FOM與占空比D的函數關系。突出顯示了目標區域。

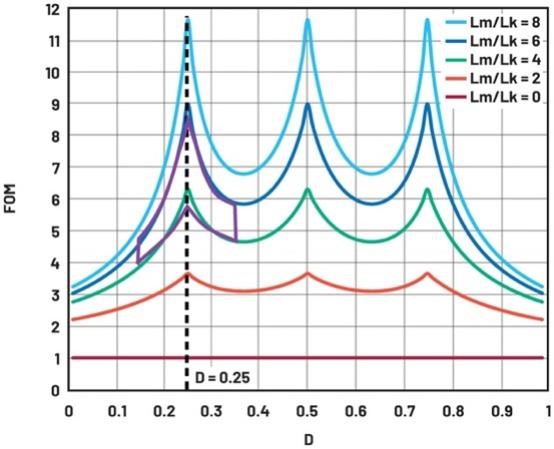

圖3.DL = 6.8 μH和CL = 4 × 1.1 μH(VIN = 48 V且Fs = 200 kHz)時的電流紋波與VO的函數關系。突出顯示了目標區域。

圖3顯示了相應的電流紋波,比較了VIN = 48 V和Fs = 200 kHz條件下的基線設計DL = 6.8 μH與建議的4相CL = 4 × 1.1 μH (Lm = 4.9 μH)。在目標區域中,CL的電流紋波與DL的電流紋波相似或更小。這意味著所有電路波形的均方根相似,傳導損耗也相似。相同Fs時的相同紋波還意味著開關損耗、柵極驅動損耗等也相同,因此這兩種解決方案的效率應該非常相似(假設DL和CL電感損耗的貢獻相似,這是唯一的區別)。

圖4.四個DL = 6.8 μH電感(上方)被替換為CL = 4 × 1.1 μH(下方),體積減小到原來的1/4。

圖5.48 V至12 V調節第一級。元件放置在PCB正面的1/4磚輪廓內。將所有~1 mm元件移至底部:1/8磚。

圖4顯示了設計的CL = 4 × 1.1 μH,其取代了四個DL = 6.8 μH電感。5每個DL的尺寸為28 mm × 28 mm × 16 mm,假設它們彼此間隔0.5 mm,那么尺寸為56.5 mm × 18 mm × 12.6 mm的4相CL可使磁元件體積減小到原來的1/4。圖5顯示了完整的1.2 kW 48 V至12 V調節解決方案,PCB單面上的元件位于1/4磚輪廓內。CL尺寸和封裝經過專門設計,兩個CL元件可以安放在行業標準四分之一磚尺寸內。將所有~1 mm元件(FET、控制器IC、陶瓷電容等)放置在PCB底部,從而實現1/8磚尺寸的1.2 kW解決方案。

性能改善

當DL = 6.8 μH電感變為CL = 4 × 1.1 μH時,電感中的電流擺率限制也改善了6倍,這有助于改善瞬態性能。除此之外,盡管磁元件總體積減少到原來的1/4,但100°C時的電感飽和額定值提高了約2倍。

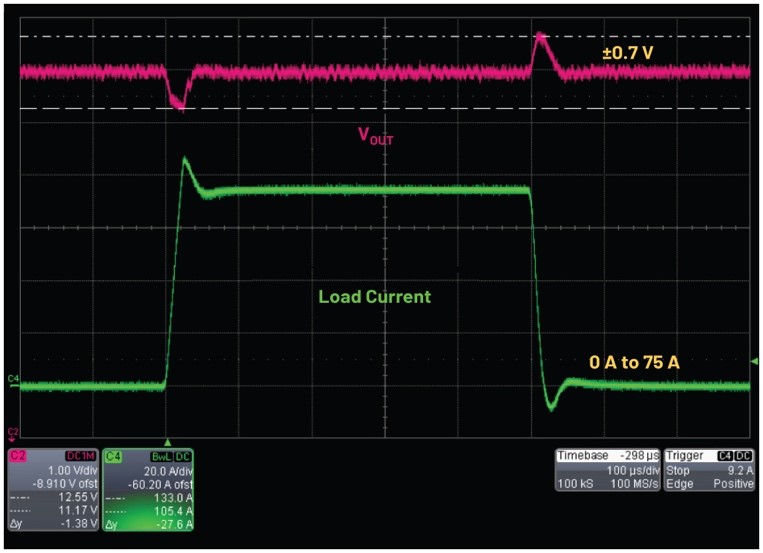

圖6顯示了建議的VIN = 48 V解決方案(輸出VO = 12 V)的瞬態性能。正如所料,對于變化的負載電流,反饋將輸出電壓調節至預設值,同時補償輸入電壓的任何變化。

圖6.75 A負載階躍下VO = 12 V輸出(CL = 4× 1.1 μH)時的瞬態性能。

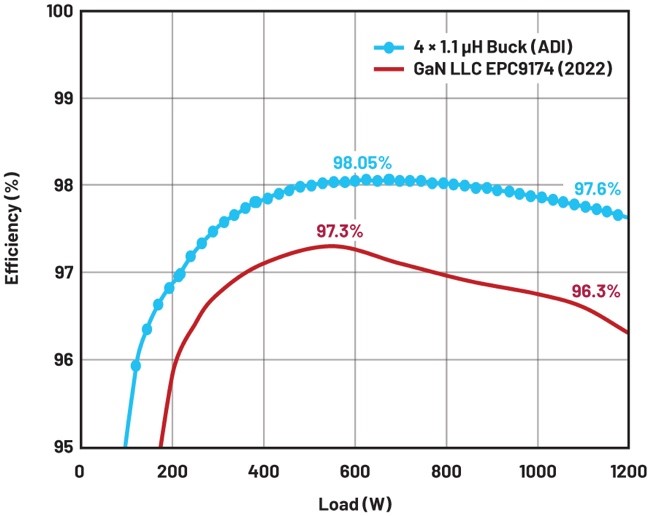

所實現的效率如圖7所示,它可能是首要的性能參數。它與先進的行業解決方案進行了比較:48 V至12 V(固定4:1降壓)LLC,初級側和次級側均有矩陣變壓器和GaN FET。10所實現的滿載效率為97.6%,而基準效率為96.3%。這意味著在全功率下損耗減少16.6 W,建議的解決方案實現了1.6倍的改進。當效率已經如此之高時,損耗要降低如此大的幅度通常很難實現。

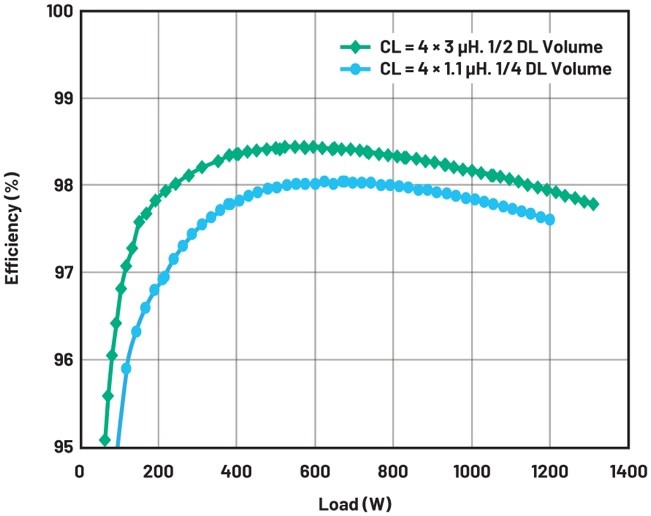

尺寸和效率之間的權衡當然是可能的。圖8比較了CL = 4 × 1.1 μH(磁元件尺寸減小到DL的1/4)和更大的CL = 4 × 3 μH(電感體積僅減小到DL的1/2)的效率。物理尺寸較大的CL = 4 × 3 μH具有較高的漏感Lk = 3 μH和較大的互感Lm = 10 μH。這使得Fs可以輕松降低至110 kHz,從而大幅提升整個負載范圍內的效率。

圖7.與1/8磚尺寸的先進48 V至12 V解決方案的效率比較。

圖8.使用耦合電感的建議48 V至12 V解決方案的效率與尺寸權衡。

結語

利用耦合電感的優勢,48 V至12 V解決方案將磁元件總尺寸減小到基本分立電感的1/4,以行業標準的1/8磚尺寸實現了1.2 kW功率。在磁元件尺寸減小4倍的同時,它保持了出色的效率性能,瞬態電感電流擺率提高了6倍,電感Isat額定值提高了2倍。

與同樣尺寸的業界先進48 V至12 V解決方案相比,它在全功率下的損耗降低了約1.6倍。如果磁元件尺寸的減小幅度可以不那么大,效率還能進一步提高。

同時,建議的解決方案提供出色的穩壓輸出,可直接放在客戶母板上,并利用標準硅FET進一步優化成本。與之相比,采用全GaN FET的非穩壓4:1 LLC是作為單獨模塊制造的,并使用具有多層、敏感布局和嵌入式矩陣變壓器的專用PCB。

整體性能改善體現了ADI耦合電感專利IP的優勢,我們很高興將其提供給眾多客戶用于DC-DC應用。

參考資料

1 Aaron M. Schultz和Charles R. Sullivan。“帶耦合感應繞組的電壓轉換器及相關方法。”美國專利6,362,986,2001年3月。

2 Jieli Li。 “DC-DC轉換器中的耦合電感設計。”碩士論文,2001年,達特茅斯學院。

3 Pit-Leong Wong、Peng Xu、P. Yang和F. C. Lee。 “采用耦合電感的交錯VRM的性能改進。”《IEEE電源電子會刊》,第16卷第4期,2001年7月。

4 Yan Dong。 “負載點應用中多相耦合電感降壓轉換器的研究。”博士論文,2009年,美國弗吉尼亞理工學院暨州立大學。

5 Alexandr Ikriannikov。 “漏感控制得到改進的耦合電感。”美國專利8,102.233,2009年1月。

6 Alexandr Ikriannikov和Di Yao。 “解決耦合電感中的鐵損問題。”Electronic Design News,2016年12月,

7 Alexandr Ikriannikov。 “耦合電感的基礎知識和優勢。”ADI公司,2021年。

8 Alexandr Ikriannikov。 “多相DC-DC應用中磁元件的演變和比較。”IEEE應用電源電子會議,2023年3月。

9 Alexandr Ikriannikov和Di Yao。 “采用多相磁元件的轉換器:TLVR與CL和新穎優化結構之比較。”PCIM Europe,2023年5月。

10 “EPC9174-評估板。”Efficient Power Conversion Corporation。

(作者:Alexandr Ikriannikov,研究員;Laszlo Lipcsei,產品應用總監)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

貿澤推出全新汽車資源中心幫助工程師了解并引領EV/HEV技術的未來

貿澤電子新品推薦:2024年第二季度推出超過10,000個新物料