【導讀】隨著電路板尺寸變小、布線密度加大以及工作頻率的不斷提高,電路中的電磁干擾現象也越來越突出,電磁兼容問題也就成為一個電子系統能否正常工作的關鍵。電路板的電磁兼容設計成為系統設計的關鍵。

導線的布局

在電路設計中,往往只注重提高布線密度,或追求布局均勻,忽視了線路布局對預防干擾的影響,使大量的信號輻射到空間形成干擾,可能會導致更多的電磁兼容問題。因此,良好的布線是決定設計成功的關鍵。

地線的布局

地線不僅是電路工作的電位參考點,還可以作為信號的低阻抗回路。地線上較常見的干擾就是地環路電流導致的地環路干擾。解決好這一類干擾問題,就等于解決了大部分的電磁兼容問題。

地線上的噪音主要對數字電路的地電平造成影響,而數字電路輸出低電平時,對地線的噪聲更為敏感。地線上的干擾不僅可能引起電路的誤動作,還會造成傳導和輻射發射。因此,減小這些干擾的重點就在于盡可能地減小地線的阻抗(對于數字電路,減小地線電感尤為重要)。

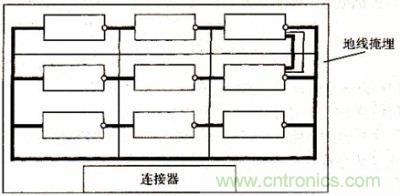

圖2:地線網絡

地線的布局要注意以下幾點:

(1)板上裝有多個芯片時,地線上會出現較大的電位差,應把地線設計成封閉環路,提高電路的噪聲容限。

(2)同時具有模擬和數字功能的電路板,模擬地和數字地通常是分離的,只在電源處連接。

(3)根據不同的電源電壓,數字電路和模擬電路分別設置地線。

(4)公共地線盡可能加粗。在采用多層厚膜工藝時,可專門設置地線面,這樣有助于減小環路面積,同時也降低了接受天線的效率。并且可作為信號線的屏蔽體。

(5)應避免梳狀地線,這種結構使信號回流環路很大,會增加輻射和敏感度,并且芯片之間的公共阻抗也可能造成電路的誤操作。

電源線的布局

一般而言,除直接由電磁輻射引起的干擾外,經由電源線引起的電磁干擾最為常見。因此電源線的布局也很重要,通常應遵守以下規則。

(1)芯片的電源引腳和地線引腳之間應進行去耦。去耦電容采用0.01uF的片式電容,應貼近芯片安裝,使去耦電容的回路面積盡可能減小。

(2)選用貼片式芯片時,盡量選用電源引腳與地引腳靠得較近的芯片,可以進一步減小去耦電容的供電回路面積,有利于實現電磁兼容。

(3)電源線盡可能靠近地線以減小供電環路面積,差模輻射小,有助于減小電路交擾。不同電源的供電環路不要相互重疊。

(4)采用多層工藝時,模擬電源和數字電源分開,避免相互干擾。不要把數字電源與模擬電源重疊放置,否則就會產生耦合電容,破壞分離度。

(5)電源平面與地平面可采用完全介質隔離,頻率和速度很高時,應選用低介電常數的介質漿料。電源平面應靠近接地平面,并安排在接地平面之下,對電源平面分布的輻射電流起到屏蔽作用。

信號線的布局

在使用單層薄膜工藝時,一個簡便適用的方法是先布好地線,然后將關鍵信號,如高速時鐘信號或敏感電路靠近它們的地回路布置,最后對其它電路布線。信號線的布置最好根據信號的流向順序安排,使電路板上的信號走向流暢。

如果要把EMI減到最小,就讓信號線盡量靠近與它構成的回流信號線,使回路面積盡可能小,以免發生輻射干擾。低電平信號通道不能靠近高電平信號通道和無濾波的電源線,對噪聲敏感的布線不要與大電流、高速開關線平行。

如果可能,把所有關鍵走線都布置成帶狀線。不相容的信號線(數字與模擬、高速與低速、大電流與小電流、高電壓與低電壓等)應相互遠離,不要平行走線。信號間的串擾對相鄰平行走線的長度和走線間距極其敏感,所以盡量使高速信號線與其它平行信號線間距拉大且平行長度縮小。

導帶的電感與其長度和長度的對數成正比,與其寬度的對數成反比。因此,導帶要盡可能短,同一元件的各條地址線或數據線盡可能保持長度一致,作為電路輸入輸出的導線盡量避免相鄰平行,最好在之間加接地線,可有效抑制串擾。低速信號的布線密度可以相對大些,高速信號的布線密度應盡量小。

在多層厚膜工藝中,除了遵守單層布線的規則外還應注意:

盡量設計單獨的地線面,信號層安排與地層相鄰。不能使用時,必須在高頻或敏感電路的鄰近設置一根地線。分布在不同層上的信號線走向應相互垂直,這樣可以減少線間的電場和磁場耦合干擾;同一層上的信號線保持一定間距,最好用相應地線回路隔離,減少線間信號串擾。

每一條高速信號線要限制在同一層上。信號線不要離基片邊緣太近,否則會引起特征阻抗變化,而且容易產生邊緣場,增加向外的輻射。

時鐘線路的布局

時鐘電路在數字電路中占有重要地位,同時又是產生電磁輻射的主要來源。一個具有2ns上升沿的時鐘信號輻射能量的頻譜可達160MHz。因此設計好時鐘電路是保證達到整個電路電磁兼容的關鍵。關于時鐘電路的布局,有以下注意事項:

(1)所有連接晶振輸入/輸出端的導帶盡量短,以減少噪聲干擾及分布電容對晶振的影響。

(2)晶振電容地線應使用盡量寬而短的導帶連接至器件上;離晶振最近的數字地引腳,應盡量減少過孔。

(3)不要采用菊花鏈結構傳送時鐘信號,而應采用星型結構,即所有的時鐘負載直接與時鐘功率驅動器相互連接。